快速的规格

PathFinder-SC的集成数据建模、提取和瞬态仿真引擎是ESD验证的端到端解决方案。单次使用模型读取行业标准设计格式,设置ESD规则,为电网提取RCs,并执行ESD模拟来分析根本原因,并提供修复和优化反馈,所有这些都在一个工具内完成。

Ansys PathFinder-SC是一个大容量的解决方案,可以帮助您规划,验证和签署IP和全芯片SoC设计的完整性和健壮性,防止静电放电(ESD)。

Ansys PathFinder-SC能够从充电设备模型(CDM)、人体模型(HBM)或其他ESD事件中识别并隔离导致芯片失效的设计问题的根本原因。它的高容量、云原生架构可以征用数千个计算核心来实现快速的全芯片周转。PathFinder-SC是由主要铸造认证的电流密度检测和ESD签收。

PathFinder-SC的集成数据建模、提取和瞬态仿真引擎是ESD验证的端到端解决方案。单次使用模型读取行业标准设计格式,设置ESD规则,为电网提取RCs,并执行ESD模拟来分析根本原因,并提供修复和优化反馈,所有这些都在一个工具内完成。

静电放电和电流密度是决定芯片在现实世界中的鲁棒性和长期可靠性的关键因素。这对产品的安全性和耐久性至关重要。

在亚16nm工艺中,降低器件击穿电压和互连尺寸会增加ESD风险。PathFinder-SC提供全面的芯片ESD事件分析,这是所有芯片设计的要求。

PathFinder-SC的全芯片容量和精简的单次使用模型可以在一次分析中同时处理数百个域。这比传统方法快得多,加快了得到结果的时间,并减少了分区导致的潜在错误。

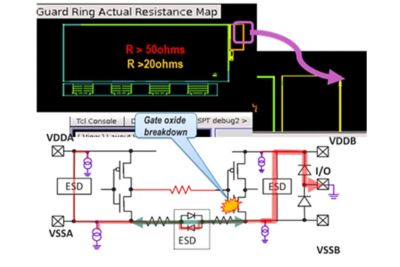

任何检测到的问题都可以通过PathFinder-SC的基于布局的分析和根本原因检测技术快速调试,再次节省时间,加快上市时间。

PathFinder-SC包括单一产品的所有功能-从执行RC提取和ESD模拟,到分析根本原因和提供优化反馈。它包括一个内置的RC提取器,不需要额外的许可证或外部工具。

PathFinder-SC是由多个客户与硅相关,并由多个铸造验证,确保准确性和降低硅风险。

Ansys PathFinder-SC帮助您计划,验证和签署IP和全芯片SoC设计的完整性和鲁棒性ESD。它识别可能导致芯片或IP故障的设计问题,包括充电设备模型(CDM)、人体模型(HBM)或其他ESD事件。PathFinder-SC通过所有主要晶圆厂的认证,确保互连的寄生,HBM/CDM ESD模拟和电流密度检查是硅精确的。它的基于布局的GUI有助于快速的根源检测和容易的调试。

PathFinder-SC采用了云原生基础架构,能够实现弹性计算,并能够处理超过1亿个晶体管的全芯片分析。

全芯片和全面的单次ESD分析和调试数百种电源模式,同时。

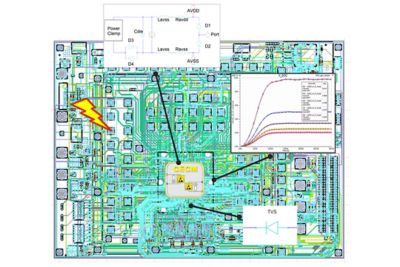

Ansys PathFinder-SC通过在电源/地面网络传播zap电流来模拟人体模型(HBM)和充电设备模型(CDM) ESD事件,以识别布局瓶颈。它模拟电流注入到任何焊盘和互连路径,以识别不能处理高ESD电流的引脚-夹脚-引脚路径。

Ansys PathFinder-SC在皮秒分辨率下使用SPICE模型和TLP曲线进行瞬态模拟,提供硅相关的精度,这有助于降低设计风险。带弹回的夹子在SPICE中经常有收敛问题;但PathFinder-SC的模拟引擎是定制的,以处理弹回和准确模型ESD设备触发。探路者的业绩已经被多个铸造厂和客户与硅联系起来。

Ansys PathFinder-SC可以识别可能导致ESD失效的布局问题和连接不平衡。例子包括没有连接到ESD夹子的凸起物,或没有连接到电源/地面的夹子。通过遍历芯片上任意两个相关点之间的每一个传导通路,PathFinder-SC验证连接的稳健性,并根据铸造或用户指定的限制检查电气特性。通过-失败报告可以交叉探测布局。

Ansys PathFinder-SC集成的数据建模、提取和仿真引擎提供了一个精简的单次ESD使用模型——在单工具环境中设置ESD规则,执行提取和ESD仿真,分析根本原因,并提供修复和优化反馈。它使用行业标准的数据格式(GDS, DEF),并在指定要检查的规则和参数方面提供了相当大的灵活性。

Ansys PathFinder-SC在IP和超过1亿实例的大型soc上检查ESD完整性。它处理数百个电源/地面/信号网络,并在单个模拟中执行电阻和电流密度检查。全芯片ESD模拟可以在几个小时到一天内完成,具体取决于大小。PathFinder-SC建立在弹性计算和云原生基础设施上,以处理超大的设计。

在标准单元级、IP级和全芯片级识别高电流热点是避免可靠性问题的关键。PathFinder-SC的内置建模能力是基于芯片ESD紧凑模型(CECM),它可以在任何级别上进行详细的ESD分析,从标准单元到全芯片。CECM包括PG模型,夹钳设备和一个可选的电流签名。这种精确的建模满足任何设计的最高可靠性需求。

Ansys PathFinder-SC建立在SeaScape大数据分析平台上,设计用于1000个CPU核上的云执行,具有接近线性的可扩展性和极高的容量,每个核的内存较低。