ANSYS的博客

2023年6月1日

尽早分析自定义ic以避免tapout延迟

Ansys收购Diakopto使半导体设计人员能够更早地发现和纠正问题

半导体公司一直在竞相开发速度更快、处理能力更强、更智能、精度更高的下一代芯片,同时将它们压缩到更小的体积中。这对集成电路(IC)设计师和布局工程师提出了一个巨大的挑战,因为曾经是电子设计自动化(EDA)的小问题现在被放大了。

芯片变小不是因为功能被移除。恰恰相反:它们被压缩了,同时将更多的功能打包到小包中。这些功能是由成千上万,数百万,甚至在某些情况下,数十亿的电线和晶体管在一个复杂的矩阵中相互连接来完成的。这种受限的布局会导致意想不到的结果,从而限制了设计的性能、可靠性和功能。高速信号的性能在很大程度上取决于单个信号线的精确特性。其中最关键的通常是使用自定义流精心制作的,以实现最佳性能。

当任何问题或性能缺陷在签字时被发现时——在集成电路可以“粘上”并发送到制造之前的最终设计验证——它会造成相当大的延迟,从而导致返工设计。对于当今复杂的半导体,验证过程可能需要相当长的时间。在重新启动流程之前,必须确定并纠正问题的原因。找到这些根本原因可能就像大海捞针,这进一步推迟了发展。

尽早调试,经常调试

为了解决这些问题,领先的电子公司正在设计过程的早期进行更多的分析。在工作流程中“左移”,尽早发现和修复潜在的挑战,不仅可以实现更有效的性能优化,而且比严格的签字验证更快地完成。理想情况下,这种分析应该足够直观,可以由许多设计师来完成,而不是由工作流程中相对较少的专家来完成,这将进一步提高效率。

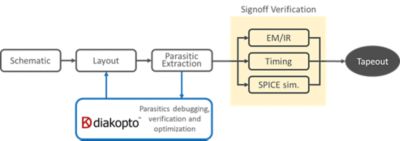

这就是Diakopto擅长的地方:早期分析,调试和优化各种高速电路,信号网络,精密模拟和电力输送网络,结合洞察力,帮助用户快速找到那些众所周知的大海捞针。该EDA解决方案提供商成立于2017年,开发的产品使IC设计和布局工程师能够快速轻松地分析定制电路,并查明导致性能瓶颈的关键因素。IC系统架构师可以利用这些发现,通过解决由布局寄生引起的关键问题,更有效地优化和调试设计。

布局寄生是一种意外的电阻和电容(RC)效应,在当今密集、高度复杂的集成电路中,这种效应变得更加显著,更有可能发生不可避免的电耦合。向更先进的硅工艺节点的迁移导致了现代集成电路中寄生元件的规模、影响和数量的指数级增长。Diakopto的ParagonX帮助设计人员将寄生相关的调试和优化时间从几天或几周减少到几分钟或几小时。ParagonX工具包集成了易于解释的可视化,并提供了一套全面的分析,包括电阻和电容/耦合分析;RC延迟、交流和瞬态仿真;网络与设备的比对与匹配验证;质量保证与验证;以及网表比较和结构分析。

说明Diakopto的技术如何通过增加对关键电路(如SERDES,数据转换器,RF,差分电路,存储器,ESD网络等)的分析来补充通用IC设计流程。

Diakopto的PrimeX增强了现有的电迁移/电压降(EM/IR)方法,使工程师能够在块级和顶层执行非常快速的电网验证。通过提供清晰、直观的结果,识别布局中的层和多边形中的弱点和瓶颈,PrimeX帮助工程师提高电路的电源完整性和可靠性,同时加快产品上市时间。

组合工作流程提供速度和准确性

该公司的产品不是为签名级别的准确性而设计的,但它们速度很快,可以多次迭代运行,并提供可操作的分析,以指导设计人员优化电路或解决他们发现的任何问题。因此,他们是一个很好的补充Ansys Redhawk-SC和Ansys图腾为数字和混合信号设计提供业界黄金标准的压降和电迁移多物理场签名解决方案。

Diakopto首席执行官兼首席技术官Maxim Ershov表示:“通过与Ansys的合作,我们相信我们可以共同解决芯片设计工作流程中更广泛的问题,加强为客户提供的产品,并推动数据中心、5G、汽车和移动应用的高科技设计创新。新闻稿.

我们欢迎Diakopto团队加入Ansys,并期待将他们的EDA专业知识添加到我们现有的销售、工程、研究和开发团队中。了解更多关于Diakopto,Ansys Redhawk-SC,Ansys图腾.

看看Ansys能为您做些什么

看看Ansys能为您做些什么

立即联系我们

谢谢你的帮助!

我们在这里回答您的问题,并期待与您交谈。我们Ansys销售团队的一名成员将很快与您联系。