ANSYS的博客

2022年7月15日

半导体功率完整性分析与仿真基础

随着半导体工艺技术的发展,人们努力从大量硅中挤出最后一点可实现的缩放,它已经追求可制造的硅工艺节点达到惊人的3纳米(nm)深度。不久前,在这样的几何形状中实现功能被认为是不可能的,这是一个巨大的工程胜利。尽管如此,在过去十年中,进一步提高芯片性能、密度和功耗的努力一直是一场多维度的工程斗争,在晶体管设计、硅层、工具和方法开发以及许多其他创新方面,节点缩放得到了艰苦奋斗的补充。

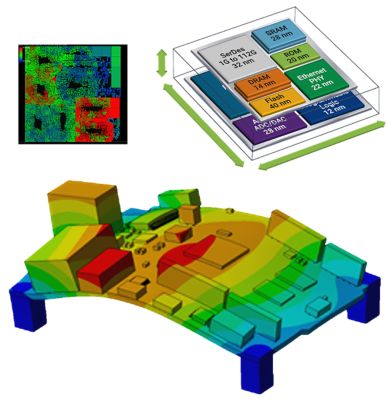

一个值得注意的例子是3D集成电路(3DIC)封装中的芯片堆叠,从一开始就是为了避免摩尔定律在超深亚微米中的脱轨。3DIC在封装和芯片层面释放出了巨大的工程创造力,但它也伴随着许多意想不到的棘手问题。

其中一个困难是在芯片上保持干净、不间断的电源分配。与信号完整性(SI)一样,功率完整性(PI)已经成为一个复杂的领域,对于理解芯片、封装和板级至关重要。

即使只是在芯片层面,距离、材料和带宽和原始速度的设计要求的影响,也会造成从MHz到GHz频率范围内的功耗和电磁干扰(EMI)场景,以及从微观到宏观的物理缩放。但是,芯片级及其所有源于工艺特征和电路设计的复杂性仅代表了这个复杂主题的第一顺序。在芯片、封装和板级上存在动态信号和电源交互。除此之外,进一步的相互作用问题上升到系统级别,系统本身之间,甚至来自更遥远的射频(RF)源。

Ansys的Norman Chang博士和Altan Odabasi博士将他们数十年的专业知识集中在这一系列PI挑战上,领导Ansys的技术工作,在芯片和封装级别对PI的各个维度进行建模和模拟。他们制作了一个按需网络研讨会,“半导体功率完整性分析与仿真基础”讨论了单片系统(SoC)设计中电压(IR)和动态压降(DVD)分析与仿真的基础。

本次网络研讨会将详细探讨多种工艺技术特点及其对电源完整性的影响。从多物理场的角度,包括热、信号和射频效应,将全面研究RLC提取和IR/DVD建模的发展。最后,将概述并深入探讨模拟这些现象的数值方法和操作。

欢迎加入我们这是我们电磁学基础系列网络研讨会的第七期也是最后一期.这个总结演讲有望成为高度技术性的网络研讨会中最深入的一个。

看看Ansys能为您做些什么

看看Ansys能为您做些什么

立即联系我们

谢谢你的帮助!

我们在这里回答您的问题,并期待与您交谈。我们Ansys销售团队的一名成员将很快与您联系。