ANSYS的博客

2022年6月2日

IR-ECO:是否有可能在不破坏芯片时序的情况下修复电压降违规?

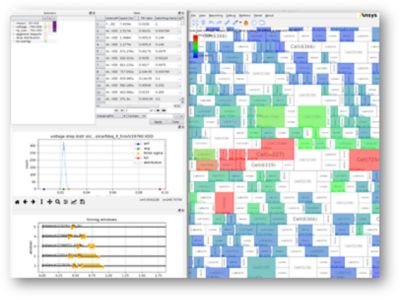

经验告诉芯片设计师,在设计过程的后期纠正电压降(IR降)问题是非常困难的.IR-ECO(工程变更订单)尤其困难,因为竞争压力总是将芯片性能推向绝对极限,而旨在解决IR下降的设计变更最终会破坏时序,从而导致更多的编辑和意想不到的后果。结果是,过去的设计人员认为有必要过度设计配电网络,以避免以后出现任何IR下降问题。

但是过度设计已经不再是当今先进硅工艺的可行选择,原因有三。

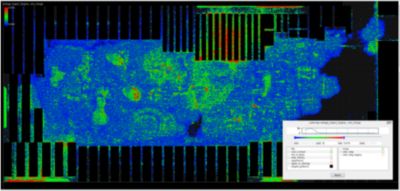

1.降低电力消耗的巨大压力导致电源电压降低,有时仅略高于半伏特。这意味着电压余量已经变得非常薄,而消除它所需的过度设计量是令人望而却步的。

2.动态电压降(DVD)的相对影响急剧增加。考虑到可能的开关场景的天文数字,由相邻电池同时开关引起的强局部电流浪涌会导致难以预测的显著瞬态电压降。

3.微型纳米级逻辑门的开关速度对电源电压非常敏感。正因为如此,即使是很小的红外衰减也会减慢通过该门的信号路径。对于已经没有空闲时间的关键计时路径,这种影响最为严重。

因此,设计人员在接近时序关闭时,会发现许多意想不到的dvd感应电压问题和时序故障。在过去,这些数量较少,IR-ECO可以通过一些人工干预来解决。如今,设计更大,频率更高,红外下降问题迅速变得太多,并且相互关联,无法进行人工干预。我们需要更好的修复指导和根本原因分析,以帮助设计人员有效地修复IR问题,从而最大限度地减少他们需要进行的更改数量。

技术,时序和电压降

需要一种技术解决方案来解决时序和电压降之间的深度依赖关系。电压降分析和静态时序分析通常是非常不同的操作,没有协调。然而,任何加速路径的尝试通常都涉及到增加更高的驱动强度门,这会消耗更多的功率,因此会产生更多的DVD。另外,可以将路径元件放置得更近以减少互连延迟,但这意味着任何本地DVD的影响都会影响同一关键路径上的多个门,从而放大时序影响。如果没有大量的人工干预,传统的电子设计自动化(EDA)流程无法解决这种相互依赖关系。

电压/时序相互依赖的一个显而易见的解决方案是简单地检查任意时序对DVD的影响ECOs在接受改变之前。不幸的是,DVD分析需要在整个修改后的设计中运行多个活动向量,这在计算上是昂贵的,并且使该解决方案的时间令人望而却步。

IR-ECO显然已经发展成为快速有效的定时签署的主要障碍,需要多次迭代和手动编辑来解决。Ansys在电压降分析和多厂商集成的开放式平台方法方面一直处于行业领先地位。

欢迎光临Ansys公司1593号展位2022设计自动化大会将于7月10日至14日在旧金山举行,以探索最新的IR-ECO思维、技术和多供应商工作流程。参加我们的早餐事件在7月12日(周二)展览开幕前,与行业专家进行小组讨论,或参加Ansys客户演示研讨会,了解Ansys多物理场解决方案和平台如何为我们的客户提供真正的成果。

看看Ansys能为您做些什么

看看Ansys能为您做些什么

立即联系我们

谢谢你的帮助!

我们在这里回答您的问题,并期待与您交谈。我们Ansys销售团队的一名成员将很快与您联系。