ANSYS的博客

2023年4月10日

在集成电路设计中减小红外降的步骤

什么是IR Drop?

在电流流动过程中,导线两端之间的电位差或电压降称为IR降(来自欧姆定律:V=IR)。在芯片中,电力和地通过构成电力输送网络(pdn)的金属网络进行分配。当电流流过PDN时,根据欧姆定律,部分电压在整个网络中下降。这种现象被称为IR下降。

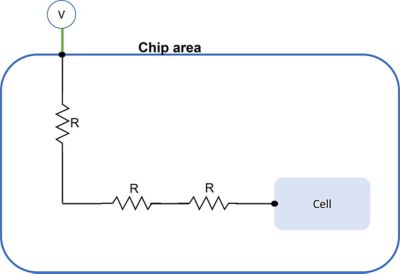

在电压达到标准电池电源引脚之前,输电网络中的电压下降会显著影响芯片的开关速度和性能。对地网的同样影响导致地反弹,即名义上的零电压上升到零以上。

由于电源引脚和电池之间的互连中的寄生电阻造成的电压下降。

随着技术节点数量的减少,芯片上晶体管的数量增加,电线变得更小。电压降较高的两个主要原因是,具有数亿个晶体管的芯片通过pdn提取大量电流,以及金属导线抵抗电流。今天的高性能芯片,如图形处理单元(gpu)可以很容易地消耗超过200w的电流,这会产生强烈的供电电流。

由于pdn中的IR下降,标准电池可能无法获得其操作所需的足够电压,从而导致性能降低。它甚至可能导致IC工作中的致命错误。在IC设计过程中,必须将IR下降对电路时序的影响作为一个重要步骤来考虑,以避免这些问题。

IR下降的类型

红外下降分为静态红外下降和动态红外下降两种。静态红外下降发生在电路不工作时,并且依赖于PDN的电阻-电容器(RC)网络。栅极通道泄漏电流是造成静态IR下降的主要原因。

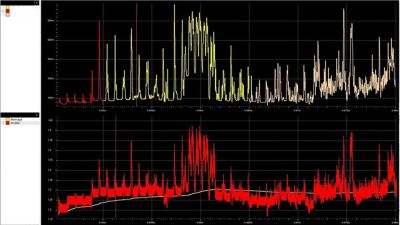

当晶体管开关时,PDN中的电压降称为动态红外下降。当许多单元以高频率同时切换时,通过PDN将吸引更多的电流。这导致波动的高电压降,被称为动态红外降。

图表显示基于时间的功率分布。

减少IR下降的最佳实践

生产设计:PDN负责将功率分配到芯片的不同部分,因此设计良好的PDN至关重要。设计良好的PDN应具有低电阻和低电感,以减小压降。PDN还应该有足够数量的电压调节器,以确保芯片的所有部分接收到所需的电压量。

EMIR分析的一个签名电源完整性的工具,如Ansys RedHawk-SC可以产生构建质量指标(BQM),测量特定PDN布局在放置之前满足电路功率需求的程度。在设计流程中,可以快速识别和早期改进供电薄弱的区域。

优化布局:通过增加金属线的宽度和在电网中使用更少的过孔,可以减少PDN中的电阻和电感,从而减少红外降。优化布局和采用高速设计准则可以帮助降低pdn中的电压降。

Ansys PowerArtist,通过估计RTL级的功率,对输电网进行优化。

正确的电源和接地平面布置:对于敏感的模拟、射频(RF)和混合信号设计,芯片中的电源和地平面在减少红外下降方面起着至关重要的作用。将电源和地平面靠近晶体管可以减少配电网络中的电阻和电感。这反过来又使ir下降最小化。

减少本地当前的需求;放置算法可以考虑附近单元所吸引的局部电流密度,并确保将它们分散得更远。这通常可以显著改善动态电压降(DVD),而不会对时序结果产生太大影响。

片上去耦电容器:片上去耦电容器的使用可以通过为高频噪声提供低阻抗路径和降低电压降来帮助最小化红外降。这些电容器应靠近晶体管的电源和接地引脚。去耦电容通过为晶体管提供局部能量源来减少红外下降,从而减少了对来自PDN的大电流的需求。

红外跌落分析工具:红外跌落分析工具可以帮助您预测和测量芯片中的红外跌落。这些工具可以提供跨芯片不同部分的电压降的可视化表示,允许您识别测量电压降的根本原因,并指出需要改进的区域。

对于任何集成电路的接线,红外降是一个重要的信号验证。减少它对于确保芯片的正确操作至关重要,通过遵循本博客中概述的步骤,您可以最大限度地减少IR下降并提高芯片的性能。请查看Ansys RedHawk-SC和Ansys PowerArtist页面,看看它们如何帮助您减少IR下降。

看看Ansys能为您做些什么

看看Ansys能为您做些什么

立即联系我们

谢谢你的帮助!

我们在这里回答您的问题,并期待与您交谈。我们Ansys销售团队的一名成员将很快与您联系。