Ansys优势杂志

日期:2020年

优化高速串行链路串扰

戴戴,美国NVIDIA圣克拉拉混合信号IC设计经理

今天的片上系统(SoC)设计——不管应用是什么——都变得越来越复杂。具体来说,当涉及到消除电磁(EM)串扰并在合理的时间内实现高效的配电网络时,高速芯片变得更加令人生畏。

举个例子:

- 汽车行业的工程师正在努力解决80 GHz毫米波雷达芯片的问题,这些芯片具有大量的芯片上EM复杂性。当然,在最终产品中安全至关重要的设备上,串扰是一个巨大的问题。

- 在5G蜂窝网络中,工程师们面临着一个电磁噩梦:同一个芯片上有很多无线电。一些团队必须在单个5G收发器上模拟5000种不同的频率互调产品。

- 设计图形处理单元(gpu)等高性能人工智能芯片的团队必须处理每秒千兆字节的输入/输出以及由此产生的噪音。

- 高带宽存储器和处理器核心必须处理连接核心和存储器的复杂多层硅中间体。

所有这些芯片都有两个共同点:高速度和高频率。

NVIDIA的NVLink技术路线图显示,吞吐量在两年内翻了一番。密集的数据链增加了串扰的风险。

在高速芯片到芯片串行链路设计方面,我们的吞吐量每两年就能翻一番,但我们必须在相同的区域内实现这一目标。这意味着更紧密的数据链接,这增加了串扰的风险。

此外,最新的GPU设计已经广泛地使用了中间体。这些干扰物会引起额外的串扰。如果你不考虑插入器,它会反过来咬你,因为你会有插入器在你的电感上产生耦合。

此外,由于较大的凸距(从150毫米到200毫米)以及在受限区域内的凸距数量有限,当您想要分离噪声功率域(例如数字功率和模拟功率域)时,可能具有挑战性。要做到这一点,你需要多个动力和地面碰撞。当你有大量的颠簸时,很难干净地布线和接地。这会恶化相声的潜力。你必须分析什么类型的耦合来自临界质量的功率和地面。

知识是关键

为了提高信号完整性和功耗,我们需要对电磁敏感。由于我们的团队不断地在高速、高频设计上突破极限,我们已经建立了一种有效的方法来根除串扰问题,而不会耽误我们的进度或占用太多的工程资源。

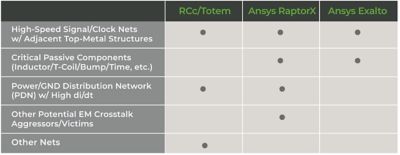

英伟达的设计方法是分层的。我们首先把所有的东西分成不同的类别,最关键的是高速信号和时钟网络。我们从传统的电阻和电容提取开始,并将耦合(RCc)提取作为顶级模拟方法的一部分。在最初的探索中,我们不需要太多的细节,但在检查高速信号和时钟网络和相邻的顶部金属结构,以及电力和地面配电网络时,我们确实需要快速的恢复时间。我们求助于Ansys Totem,它可以进行电网弱点分析,点对点检查,以及各种早期静态和动态IR和EM分析,可以突出设计弱点。

为了在方法中进行额外的分析和优化,团队依靠Ansys RaptorX和Ansys Exalto来检查高速信号和时钟网络;关键的被动器件,如t型线圈、电感器和凸点;动力:接地;以及其他可能导致电磁相声的攻击者和受害者。

RaptorX是一款布局后的RLCk提取软件解决方案,可使IC设计工程师准确预测信号停止阶段的电磁耦合效应。它可以通过提取集总单元寄生并生成精确的电、磁和衬底耦合模型来捕获设计层次结构中不同块之间的未知串扰。而Exalto将上述功能与传统的RC提取流程集成在一起,使设计人员更容易使用。

让我们来看看一些例子,看看我们如何在设计的各个部分实现探索串扰的方法,然后根据结果优化这些设计。

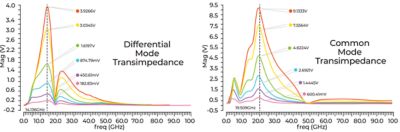

图中显示了从电力输送网络到敏感接收机信号网络的差分和共模串扰与有效去耦电容器的对比。图中不同的颜色意味着在配置中使用了不同数量的decap。

数据路径串扰分析

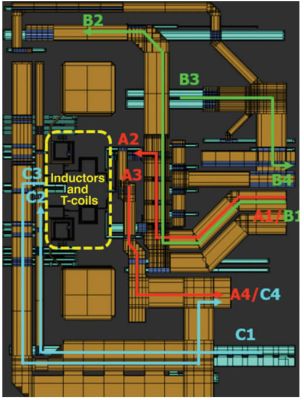

下图是NVIDIA GPU最新设计的高速接收器的部分平面图。由于面积的限制和功率效率的考虑,与传统的射频设计相比,电感器和t型线圈有一个有限的保持区域。你不能为这些无源结构提供一个大的区域,因为你必须把所有的高速电路都隔开。这反过来又使您的整体设计功耗低。为了捕获相邻的串扰效应,我们使用RaptorX提取所有关键网络和相邻的电源/接地作为n端口,部分布局仅包括顶部的厚金属层。

我们提取了整个区域作为模型。我们将不同的端口放在不同的位置,并进行了s参数仿真和瞬态仿真来确定串扰的影响。一旦我们有了结果,我们重新优化了布局和去耦电容(decap)放置,以最小化串扰效应。

我们希望通过在正确的位置放置decaps来减少感兴趣频率上的串扰效应2-10倍;从底部的暂态波形可以看出,优化后的暂态效应减小到3毫伏。它仍然存在,但我们根据分析将影响降到最低。

功率时钟线路挑战

另一个大问题是从电源到高速时钟线的串扰。使用SerDes(序列化器/反序列化器)设计,通常一个锁相环(PLL)将把关键的高速时钟驱动到多个不同的数据通道。这个时钟分布可以运行几毫米,具体取决于应用程序。由于面积的限制,很难避免有噪声的地面和电源与时钟线平行运行。即使你在时钟的侧面有适当的屏蔽,这也是不够的。你仍然会遇到来自这些电线的严重磁串扰。

为了捕捉全局,您必须将多个数据通道放在一起,以包括整个时钟分布网络。为此,您需要提取超过50个,有时甚至多达100个端口。只有RaptorX才能做到这一点。

NVIDIA GPU设计中高速接收器的局部平面图显示了片上无源组件(电感器/ t型线圈)的有限保留区域。

当你使用RaptorX从电源、地线和时钟中提取整个东西时,你会看到来自电源和地线的更严重的串扰抖动。

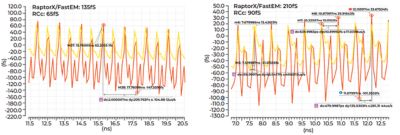

这两个对比图可以让NVIDIA查看抖动。他们在不同的地方展示了相同的模拟。黄色的是基于碾压混凝土提取的。

即使在优化之后,我们看到的瞬时抖动是只有rcc的数字的两倍。这种影响很难完全消除,但通过适当的设置和工具,您可以预测它,并将其与其他随机抖动(RJ)和确定性抖动(DJ)一起包含在抖动预算中。如果你忽略了这一点,当硅回来的时候,你会有一个惊喜。我们需要这个Ansys工具来确保我们从这种耦合中捕获所有的效果。

NVIDIA可以通过两种比较图来观察抖动。他们在不同的地方展示了相同的模拟。黄线是基于碾压混凝土提取。

如何优化配电

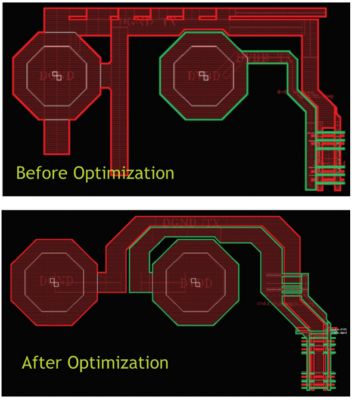

下图是我们使用RaptorX和Exalto组合执行的电力传输网络(PDN)的优化。我们的分析包括感应顶部金属层以及底部电阻下通孔和金属。我们在所有接入点上都设置了端口,包括凸起、解耦帽、电流汇聚和源。

decaps经过优化,以减少对高频电流输送的长顶部金属线路的依赖,同时保持高面积效率。电流返回路径与传递路径并行仔细规划,以最大限度地减少环路包围和降低磁通/路由电感。

RaptorX使NVIDIA能够提取较长的时钟路由,加上多个通道上的功率传输网络

端口个数。

通过这种优化,我们能够将di/dt(电流变化率)引起的电源纹波降低40%。

规模效率

使用先进的SerDes设计,随着频率的不断增加,简单的RCc提取无法捕获高速损伤。这些损伤包括电磁串扰和di/dt诱导的电源噪声。

NVIDIA使用Ansys RaptorX和Ansys Exalto来优化电力输送网络。

我们使用RCc和EM工具的组合来正确地建模所有这些。使用RaptorX和Exalto,我们能够在短时间内高效地进行非常大规模的提取,这使我们能够将物理设计推向极限,同时将相关风险降至最低。最终的结果是一个节能的设计。

看看Ansys可以为您做什么

看看Ansys可以为您做什么

今天就联系我们

谢谢你的联系!

我们在这里回答你的问题,期待与你交谈。我们Ansys销售团队的一名成员将很快与您联系。